# ICs for Communications

Quadrature Phase Modulator PMB 2205

Data Sheet 01.94

| PMB 2205<br>Revision History: | 01.94         |  |

|-------------------------------|---------------|--|

| Previous Releases:            | 04.92 / 07.92 |  |

| Page                          | Update        |  |

|                               |               |  |

### **Data Classification**

#### **Maximum Ratings**

Maximum ratings are absolute ratings; exceeding only one of these values may cause irreversible damage to the integrated circuit.

### Characteristics

The listed characteristics are ensured over the operating range of the integrated circuit. Typical characteristics specify mean values expected over the production spread. If not otherwise specified, typical characteristics apply at  $T_A = 25$  °C and the given supply voltage.

### **Operating Range**

In the operating range the functions given in the circuit description are fulfilled.

For detailed technical information about "**Processing Guidelines**" and "**Quality Assurance**" for ICs, see our "**Product Overview**".

#### Edition 01.94

This edition was realized using the software system FrameMaker<sup>®</sup>.

# Published by Siemens AG, Bereich Halbleiter, Marketing-Kommunikation, Balanstraße 73, D-81541 München.

© Siemens AG 1994. All Rights Reserved.

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

For questions on technology, delivery and prices please contact the Semiconductor Group Offices in Germany or the Siemens Companies and Representatives worldwide (see address list).

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Siemens Office, Semiconductor Group.

Siemens AG is an approved CECC manufacturer.

#### Packing

Please use the recycling operators known to you. We can also help you - get in touch with your nearest sales office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport.

For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice you for any costs incurred.

# **Quadrature Phase Modulator**

### PMB 2205

**Bipolar IC**

### **Preliminary Data**

### Features

- Double-balanced mixers

- Direct modulation

- Linear modulating inputs

- Symmetrical circuitry

- Generation of orthogonal carriers within a wide frequency range

- LO operation alternatively at transmit frequency  $(f_0)$  or double transmit frequency  $(2 f_0)$

- Output of frequency doubler may be filtered by external tank circuit

- 35 dB carrier rejection, 40 dB SSB rejection

- 42 dB rejection of third order products at normal drive level

- 38 dB rejection of doubled RF output frequency

- 0 dBm linear output power

- Power ON/OFF switch, low standby current

- LO frequency range 120 MHz to 800 MHz at LO, LO input

- Double transmit frequency range 80 MHz to 900 MHz at PP/PP input

- Modulation frequency range 0 to 400 MHz

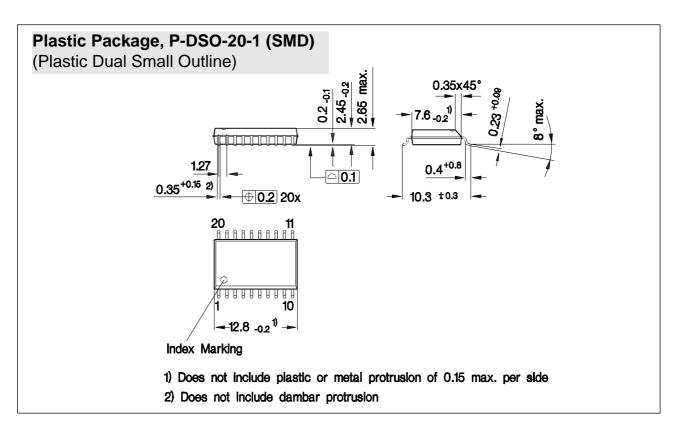

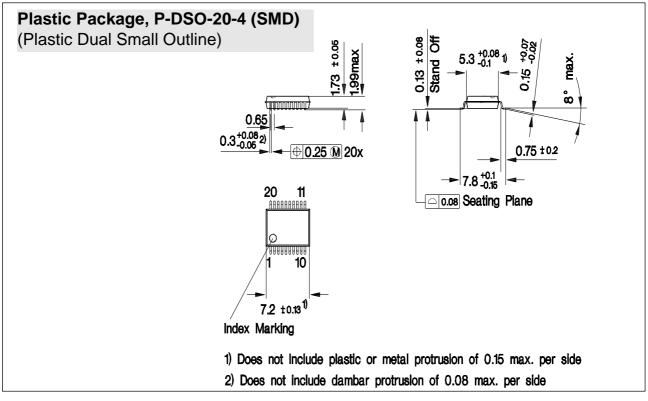

- P-DSO-20-1; P-DSO-20-4 package

- Temperature range 25 °C to 85 °C

| Туре      | Version | Ordering Code | Package                 |

|-----------|---------|---------------|-------------------------|

| PMB 2205T | V1.1    | Q67000-A6048  | P-DSO-20-1 (SMD)        |

| PMB 2205S | V1.1    | Q67000-A6066  | P-DSO-20-4 (SMD Shrink) |

| PMB 2205T | V1.2    | Q67000-A6083  | P-DSO-20-1 (SMD)        |

| PMB 2205S | V1.2    | Q67000-A6084  | P-DSO-20-4 (SMD Shrink) |

For new designs V1.2 has to be used.

### P-DSO-20-1

### Applications

- Digital mobile radio and WLAN

- PCN & GSM-systems

- Continuous phase modulation, e.g. GMSK

- Various kinds of QPSK modulation and linear QAM

- Frequency fine tuning

- Image reject up and down mixer

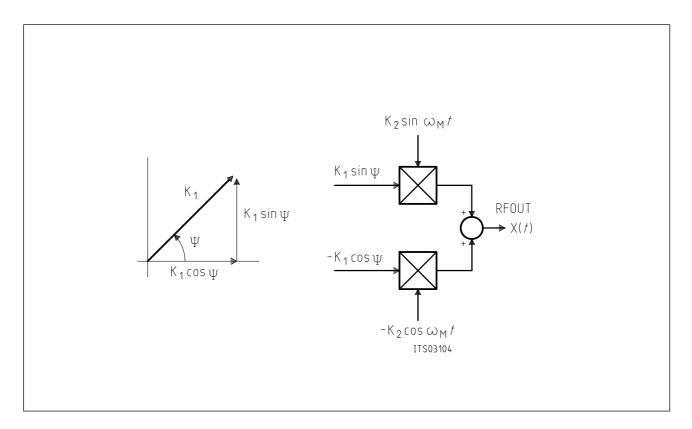

The phase  $\Psi(t) - \omega_M t$  of RF-carriers in the range 120 to 800 MHz is modulated by external signals  $I(t) = K_2 \sin \omega_M t$  and  $Q(t) = -K_2 \cos \omega_M t$ . The circuit is to be incorporated into a transmitter for mobile telephones conforming to the PCN/GSM standards.

$\mathsf{X}(t) = \mathsf{K}_1 \sin \Psi(t) \ge \mathsf{K}_2 \sin \omega_{\mathsf{M}} t + \mathsf{K}_1 \cos \Psi(t) \ge \mathsf{K}_2 \cos \omega_{\mathsf{M}} t$

=  $K_1 K_2 \cos (\Psi(t) - \omega_M t) \rightarrow \text{lower sideband}$

Realization to eq.(8) in GSM rec. 05. 04. Feb. 88

The actual internal generated orthogonal LO carriers work in switching mode.

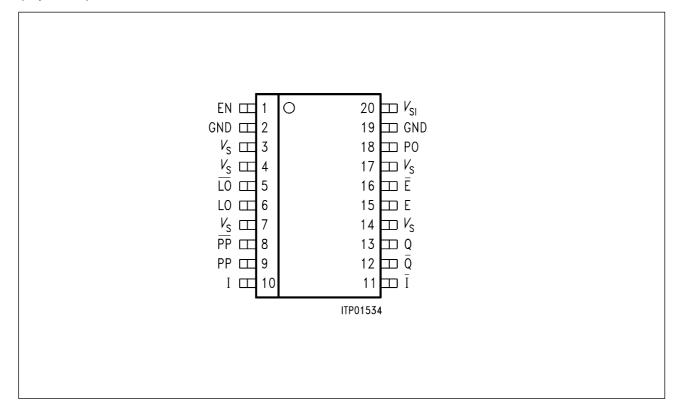

### **Pin Configuration**

(top view)

### **Pin Definitions and Functions**

| Pin No. | Symbol          | Function                                                                                                                   |

|---------|-----------------|----------------------------------------------------------------------------------------------------------------------------|

| 1       | EN              | Enable, power ON/OFF switch                                                                                                |

| 2       | GND             | Ground                                                                                                                     |

| 3       | Vs              | Supply voltage                                                                                                             |

| 4       | Vs              | Supply voltage, connected to pin 3                                                                                         |

| 5       | LO              | Local oscillator frequency input, inverted                                                                                 |

| 6       | LO              | Local oscillator frequency input                                                                                           |

| 7       | Vs              | Supply voltage, connected to pin 3                                                                                         |

| 8       | PP              | Tank circuit or double transmit frequency input, inverted                                                                  |

| 9       | PP              | Tank circuit or double transmit frequency input                                                                            |

| 10      | I               | Modulating input I, open base                                                                                              |

| 11      | Ī               | Inverted modulating input Ī, open base                                                                                     |

| 12      | Q               | Inverted modulating input $\overline{Q}$ , open base                                                                       |

| 13      | Q               | Modulating input Q, open base                                                                                              |

| 14      | Vs              | Supply voltage, connected to pin 3                                                                                         |

| 15      | E               | RF output, open collector                                                                                                  |

| 16      | Ē               | Inverted RF output, open collector                                                                                         |

| 17      | Vs              | Supply voltage, connected to pin 3                                                                                         |

| 18      | PO              | Output emitter source resistor of output stage, to be connected to GND direct or via a resistor to program emitter current |

| 19      | GND             | Ground, connected to pin 2                                                                                                 |

| 20      | V <sub>SI</sub> | Test output of internal bias voltage                                                                                       |

### \_

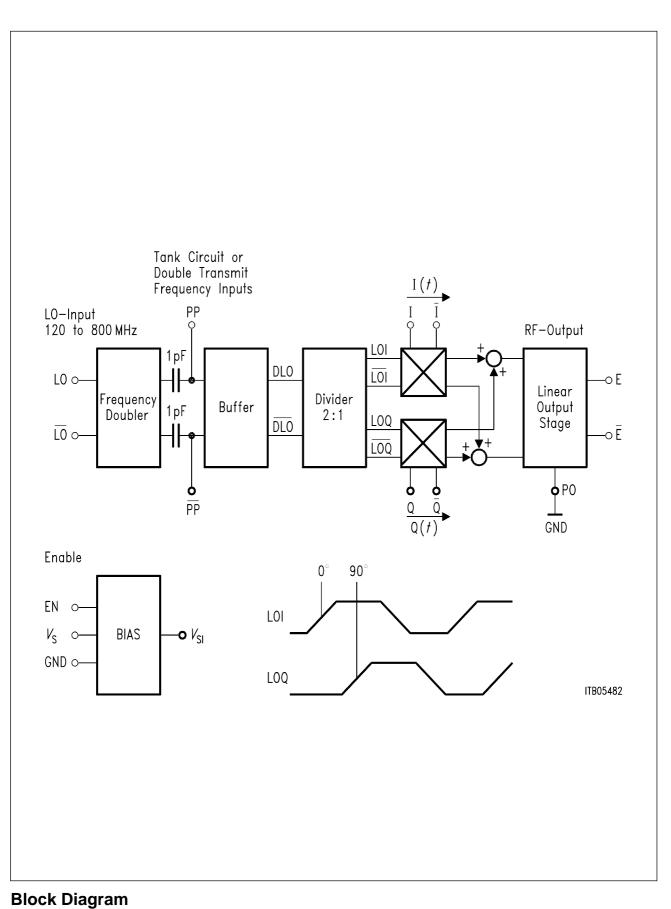

### **Circuit Description**

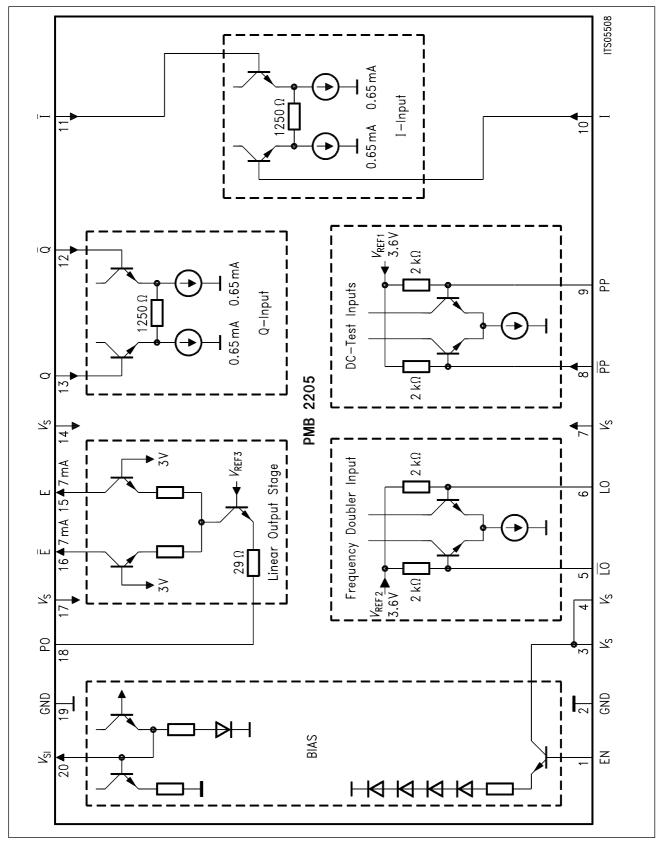

The transmission frequency  $f_0$  at the differential inputs LO,  $\overline{\text{LO}}$  is first doubled and then bandpass filtered at  $2f_0$ .

The filter may be realized by an external tank circuit at PP,  $\overline{PP}$  providing a high suppression at higher harmonics than  $2f_0$ . Alternatively, a local oscillator operating at 2  $f_0$  may be connected to PP,  $\overline{PP}$  while LO,  $\overline{LO}$  is RF grounded.

This frequency is the clock for a 2:1 divider. At the outputs of the two latches of this divider orthogonal carriers LOI and LOQ for the modulator are provided. The modulator consists of two Gilbert Multipliers which are operated in switching mode by LOI and LOQ respectively. Furthermore these multipliers are driven with high linearity by the modulating signals I(t) and Q(t) up to 1.5 Vpp.

The output signals of both Gilbert cells are combined at the addition points. The sum drives a linear output stage.

An internal current source resistor of the output stage is fed to PO. This pad should be connected to GND when minimal nonlinear distortion and maximum output power is desired.

Alternatively a resistor can be inserted, e.g. 30  $\Omega$ , in order to reduce the output current by half.

The pin  $V_{SI}$  is used for DC-testing. A power-down switch EN reduces the current consumption from approximately 40 mA in the active mode to less than 10  $\mu$ A in the standby mode.

### **Electrical Characteristics**

### **Absolute Maximum Ratings**

$T_{\rm A}$  = - 25 to 85 °C

| Parameter                                           | Symbol            | Limit             | Unit |     |

|-----------------------------------------------------|-------------------|-------------------|------|-----|

|                                                     |                   | min.              | max. |     |

| Supply voltage                                      | Vs                | - 0.5             | 7    | V   |

| Differential input voltage (any differential input) | $V_{Diff}$        | - 3               | 3    | V   |

| Output voltage at E and $\overline{E}$              | V <sub>OUT</sub>  | $V_{\rm S} - 1.6$ | 7    | V   |

| Junction temperature                                | Tj                |                   | 125  | °C  |

| Storage temperature                                 | T <sub>stg</sub>  | - 55              | 125  | °C  |

| Thermal resistance P-DSO-20-1                       | $R_{ m thJA}$     |                   | 90   | K/W |

| Thermal resistance P-DSO-20-4                       | R <sub>thJA</sub> |                   | 143  | K/W |

### **Operational Range**

Within the operational range the IC operates as described in the circuit description. The AC/DC characteristic limits are not guaranteed

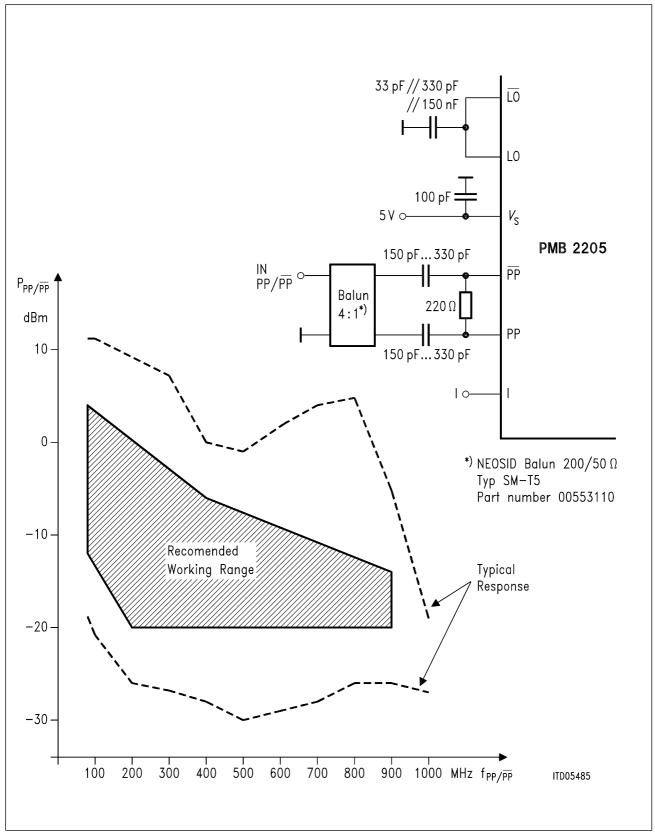

| Double transmit frequency input level                  | $P_{\rm PP/\overline{PP}}$ | see input sensitivity<br>diagram figure 3 |     |     |  |

|--------------------------------------------------------|----------------------------|-------------------------------------------|-----|-----|--|

| Double transmit frequency range at PP/PP               | $f_{\rm PP/\overline{PP}}$ | 80                                        | 900 | MHz |  |

| Transmit frequency input level referred to 50 $\Omega$ | $P_{\text{LO/LO}}$         | - 12                                      | 0   | dBm |  |

| Transmit frequency range at LO/LO                      | $f_{\rm LO/\overline{LO}}$ | 120                                       | 800 | MHz |  |

| Ambient temperature                                    | T <sub>A</sub>             | - 25                                      | 85  | °C  |  |

| Supply voltage                                         | Vs                         | 4.4                                       | 5.8 | V   |  |

The pins E,  $\overline{E}$ , PP and  $\overline{PP}$  have no additional internal ESD protection circuitry

### **AC/DC Characteristics**

$V_{\rm S}$  = 5.0 V;  $T_{\rm A}$  = 25 °C;  $P_{\rm LO}$  = – 15 dBm (referred to test circuit)

| Parameter                                              | Symbol                                                                 | Limit Values |      |      | Unit | Test Condition    |

|--------------------------------------------------------|------------------------------------------------------------------------|--------------|------|------|------|-------------------|

|                                                        |                                                                        | min.         | typ. | max. |      |                   |

| Supply Current                                         |                                                                        |              |      |      |      |                   |

| Normal operation                                       | $I_{E} + I_{\overline{E}}$                                             | 11.5         | 14.5 | 18   | mA   | EN = H            |

| Normal operation                                       | Is                                                                     | 23           | 27.5 | 33   | mA   | EN = H            |

| Powered down                                           | Is                                                                     |              | 0.15 | 10   | μA   | EN = L            |

| Transmit Frequency I                                   | nput LO/Ī                                                              | 0            |      |      | 1    |                   |

| Internal DC voltage at the input bases                 | $\begin{array}{c} V_{\rm DCLO} \\ V_{\rm DC\overline{LO}} \end{array}$ | 3.3          | 3.6  | 3.8  | V    | $V_{\rm S}$ = 5 V |

| Differential AC input<br>impedance at<br>400 MHz *     | R <sub>LO/LO</sub>                                                     |              | 1.8  |      | kΩ   |                   |

| Input capacitance parallel to $R_{LO/LO}$ at 400 MHz * | $C_{\rm LO/LO}$                                                        |              | 0.8  |      | pF   |                   |

| Double Transmit Free                                   | quency In                                                              | out PP/      | PP   |      |      |                   |

| Internal DC voltage at the input bases                 | $V_{ m DCPP}$<br>$V_{ m DCPP}$                                         |              | 3.6  |      | V    | $V_{\rm S}$ = 5 V |

| Differential AC input<br>impedance at<br>800 MHz *     | R <sub>PP/PP</sub>                                                     |              | 190  |      | Ω    |                   |

| Input capacitance parallel to $R_{PP/PP}$ at 800 MHz   | $C_{\rm PP/\overline{PP}}$                                             |              | 1.8  |      | pF   |                   |

|                                                        |                                                                        |              | 1    | 1    | 1    |                   |

\* Design hint

## AC/DC Characteristics (cont'd)

$V_{\rm S}$  = 5.0 V;  $T_{\rm A}$  = 25 °C;  $P_{\rm LO}$  = -15 dBm (referred to test circuit)

|                     |              |      |      |      | 1 |  |

|---------------------|--------------|------|------|------|---|--|

|                     |              | min. | typ. | max. |   |  |

| Modulation Inputs I | to Ī and Q t | o Q  |      |      |   |  |

| Input bias current of the open bases at I, $\overline{I}$ , Q, $\overline{Q}$ **                                 | I <sub>B</sub>              | 4          | 6   | 8          | μA     |                                                                 |

|------------------------------------------------------------------------------------------------------------------|-----------------------------|------------|-----|------------|--------|-----------------------------------------------------------------|

| External DC reference at I, $\overline{I}$ and Q, $\overline{Q}$                                                 | $V_{REF}$                   | 2.1<br>2.1 |     | 2.6<br>3.2 | V<br>V | $V_{\rm S}$ = 4.5 V<br>$V_{\rm S}$ = 5.5 V                      |

| Differential input<br>swing for linear<br>output power*                                                          | V <sub>I, Q</sub>           |            | 1.0 |            | Vpp    |                                                                 |

| Differential input swing for 3 dB compression                                                                    | $V_{I,Q}$                   |            | 1.9 |            | Vpp    |                                                                 |

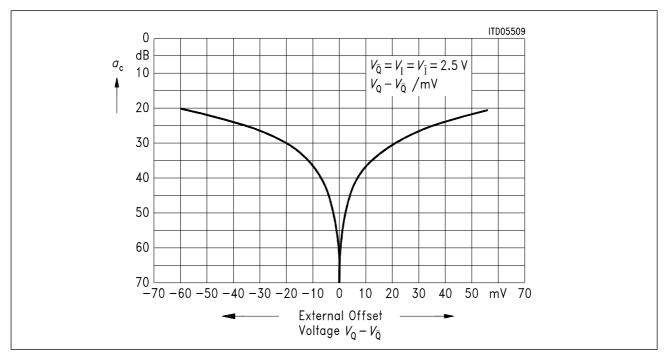

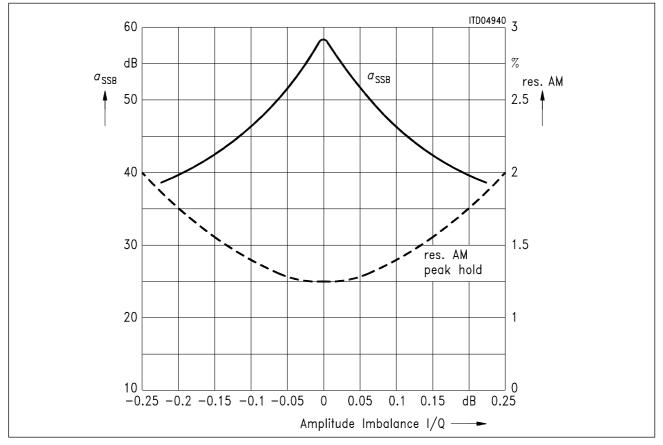

| External differential input offset voltage at I, $\overline{I}$ and Q, $\overline{Q}^*$                          | $V_{ m offset}$             |            |     | 10         | mV     | For 35 dB carrier suppression, <b>see figure 1</b>              |

| External amplitude<br>imbalance of I, Q<br>modulation signals *                                                  | $V_{\rm I}/V_{\rm Q}$       |            |     | 0.15       | dB     | For single sideband<br>suppression 40dB,<br><b>see figure 2</b> |

| Phase error of I, Q<br>modulation signals *                                                                      | $\Delta \phi_{\text{I, Q}}$ |            |     | 1          | deg    | For single sideband suppression 40dB                            |

| Differential input<br>impedance at the<br>ports I, $\overline{I}$ ; Q, $\overline{Q}$ : 1 pF<br>parallel $R_{I}$ | R                           |            | 140 |            | kΩ     | <i>f</i> = 100 kHz                                              |

| I, Q baseband input<br>frequency range: 0 Hz<br>up to the 3 dB point *                                           | f                           |            |     | 400        | MHz    |                                                                 |

\* Design hint

\*\* To avoid offset voltages, the base input should have identical bias

## AC/DC Characteristics (cont'd)

$V_{\rm S}$  = 5.0 V;  $T_{\rm A}$  = 25 °C;  $P_{\rm LO}$  = -15 dBm (referred to test circuit)

| Parameter                                              | Symbol           | Limit Values |      | Limit Values |     | ymbol Limit Values                            |  | Unit | Test Condition |

|--------------------------------------------------------|------------------|--------------|------|--------------|-----|-----------------------------------------------|--|------|----------------|

|                                                        |                  | min.         | typ. | max.         |     |                                               |  |      |                |

| Output E/E (open colle                                 | ectors)          |              |      |              |     |                                               |  |      |                |

| Output power at 3 dB<br>Compression *                  | P <sub>out</sub> |              | 6    |              | dBm | V <sub>I, Q</sub> = 1.9 Vpp                   |  |      |                |

| Linear output power at 200 $\Omega$ load, low spurious | P <sub>out</sub> | -2           | 1    | 4            | dBm | V <sub>I, Q</sub> = 1 Vpp<br>see test circuit |  |      |                |

| •                                 |                  |    |    |    |                                                             |

|-----------------------------------|------------------|----|----|----|-------------------------------------------------------------|

| Rejection of third order products |                  |    | 42 | dB | V <sub>I, Q</sub> = 1 Vpp                                   |

| Carrier suppression see figure 1  | a <sub>c</sub>   | 32 | 35 | dB | $V_{I, Q} = 1 \text{ Vpp}$<br>no external offset<br>voltage |

| Single sideband suppression **    | a <sub>SSB</sub> | 40 | 42 | dB | see test circuit                                            |

| Residual AM                       |                  |    | 2  | %  | see figure 2                                                |

### **Power ON/OFF Switching**

| Input voltage at EN<br>Active<br>Powered down | $V_{EN}  onumber V_{EN}$ | 4.2<br>0 |     | V <sub>S</sub><br>0.8 | V<br>V   | EN = H<br>EN = L           |

|-----------------------------------------------|--------------------------|----------|-----|-----------------------|----------|----------------------------|

| Input current at EN                           | $I_{\sf EN}$             |          | 30  | 80<br>0.1             | μΑ<br>μΑ | EN = H<br>EN = L           |

| Power up/down time                            | t <sub>S</sub>           |          | 1.0 |                       | μs       | $EN = H \leftrightarrow L$ |

\* Design hint for matched output

\*\* 90° phase shift between I and Q

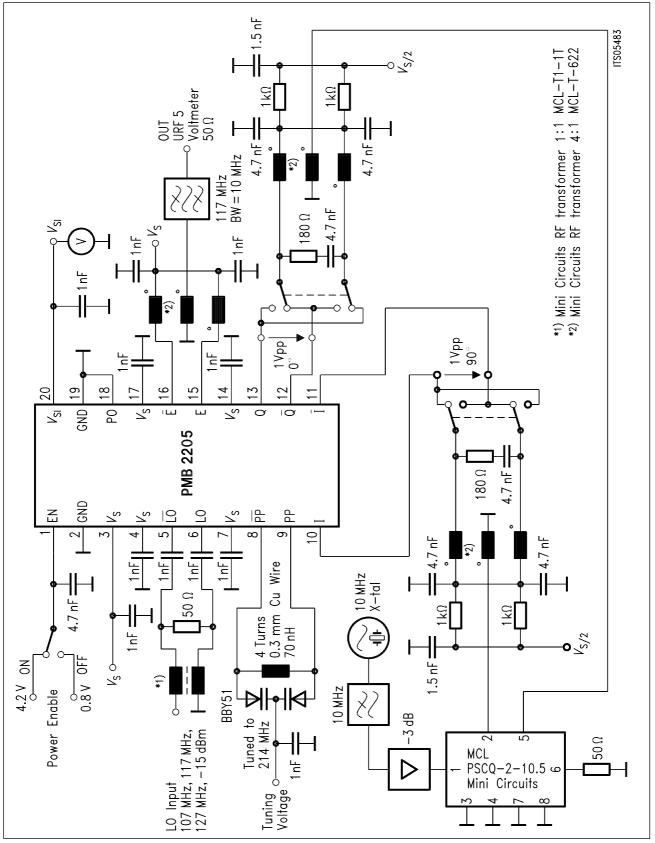

Test Circuit

RF Test Circuit for SSB Sine Modulation Test and for Applications as Image Reject up Mixer

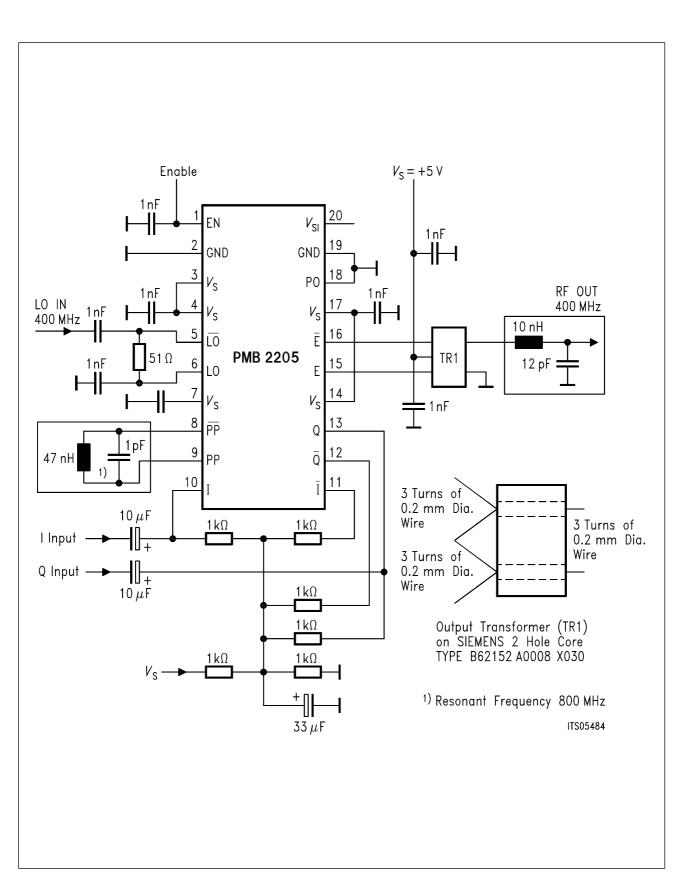

## **Typical Application Circuit**

PMB 2205

Figure 1 Carrier Suppression  $a_c$  versus Offset at Q,  $\overline{Q}$

### Figure 3 Input Level at PP, $\overline{\rm PP}$ versus Double Transmit Frequency $f_{\rm PP/\overline{PP}}$

Figure 4 PMB 2205 – Input/Output Circuitry

### Sorts of Packing

Package outlines for tubes, trays etc. are contained in our Data Book "Package Information" SMD = Surface Mounted Device

Dimensions in mm